-

乱序执行 编辑

在计算机工程领域,乱序执行(错序执行,英语:out-of-order execution,简称OoOE或OOE)是一种应用在高性能微处理器中来利用指令周期以避免特定类型的延迟消耗的范式。在这种范式中,处理器在一个由输入数据可用性所决定的顺序中执行指令,而不是由程序的原始数据所决定。在这种方式下,可以避免因为获取下一条程序指令所引起的处理器等待,取而代之的处理下一条可以立即执行的指令。

但如果采用三个人分别用三张纸同时写的做法, 那么B和C都不必须等待就可以同时各写各的了,甚至C和B还可以比A先写好也没关系(就象乱序执行),但当他们都写完后就必须重新在横幅上(自然可以由别人做,就象CPU中乱序执行后的重新排列单元)按"春节联欢晚会"的顺序排好才能挂出去。

WinChip的性能表现看到一个带有大容量一级Cache的按序执行CPU能够同乱序执行CPU竞争,在时钟周期方面,Cache未命中的代价是非常高昂的。带有大容量一级Cache的按序执行CPU性能,比只有较小容量Cache乱序执行CPU的性能要强。

而Rise的工程师在这方面犯了错误,MP6的一级Cache只有16KB,因此Cache未命中的发生频率比其他CPU高,以致于它很难“喂饱”它的3条流水线。这是很可惜的事,因为一个按序执行CPU不是太复杂,因此可以做得更小。如果Rise CPU具有较大的一级Cache和高时钟频率,那么,对于像K6-2那样的乱序执行CPU来说,Rise CPU是一个凶狠的对手,它具有更好的浮点性能(双FPU流水线),而且成本也更便宜。集成256KB二级Cache的mP6-Ⅱ或许将纠正这个错误,但它要达到令人满意的时钟频率。

由于K7采用大容量缓冲,因此它能及时发布足够多的非依赖性指令。大容量一级Cache、大容量缓冲和乱序执行,使K7的两条FPU流水线比Rise mP6的两条流水线更容易“喂饱”,效率更高。

直到大约1993年前,大多数CPU一次只能处理一条指令。那时,如果采用流水线设计,譬如摩托罗拉68040或者英特尔80486,那么可以同时在不同执行阶段处理不同的指令。

到了1991年和1992年,出现了MIPS R4000、Alpha 21064和奔腾这些处理器,它们属于面向通用市场的第一批“超标量”处理器:每个CPU周期可以处理(读取、执行及退出)两条指令。

后来,1995年出现了Alpha 21264,就有了每个周期能处理四条指令的第一个CPU,时钟频率达到300MHz,这个速度在当时十分惊人。Alpha21664在微处理器论坛上一亮相,就引来了台下观众的一片赞叹,其中包括英特尔和IBM的设计者,更不用说Sun SPARC的设计者了。遗憾的是,Alpha最后没有成功。

不管怎样,这些厂商当时都采用了有条不紊的有序执行技术(In Order):程序指令在执行时,按顺序读取、执行及引退操作码,每次执行两条或者四条指令。

不同指令需要不同的执行资源,而且程序流程往往是这样:执行需要等资源被释放出来,或者指令依赖性(dependency)得到解决,才能继续执行下一条指令。更糟的是,每出现新一代CPU,就需要重新编译代码,针对新CPU进行优化,不然读/写指令之间很可能会出现太多气泡(bubble)即空闲时间,导致性能提升幅度不大,与竞争产品相比优势也不大。

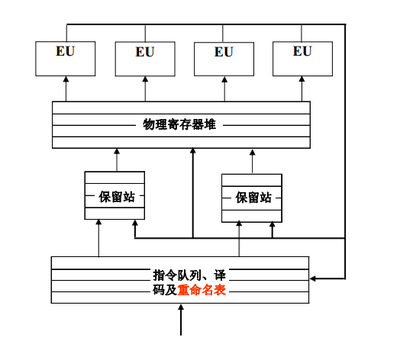

这时候,乱序执行(out of order execution)出场了。CPU硬件本身在读取指令后重新安排指令的执行顺序,根据现有资源情况,提供更多的执行单元、重新命名寄存器、处理好指令依赖性等等。所以,Pentium Pro和Alpha 21264之后的几乎所有新款CPU都是采用无序执行技术。

在多数情况下,乱序执行可以加快芯片的运行速度,有时候加速明显。21264的速度就是21164的将近两倍,而Pentium Pro的速度也比奔腾快了一大截。经过重大改进的最新MIPS架构R10000也采用了乱序执行。

从安腾到Power6

乱序执行一直发展良好,直到后来英特尔推出了一种全新的技术。意义重大的安腾处理器拥有真正独一无二的引擎,并使用了重要的显式并行指令计算(EPIC)技术。先不说安腾处理器的超过100种的指令格式组合、庞大的慢速寄存器组等,它实际上重新采用了有序执行技术。所以,编译器不得不完成所有工作,以确保执行单元始终处于忙碌状态。除了浮点处理密集型应用外,要做到这一点并非易事,只要看看安腾系统的基准测试结果就会明白。

在后续的发展中,安腾架构的这一做法从来没有变过。相反,Sun一度改用了富士通公司使用无序技术的SPARC64,而不是它自己的使用有序技术的UltraSPARC IV。其他的重要架构如x86则继续采用无序技术,使用了Core 2和K10等新引擎,并进一步改进了这种方案,以便充分利用每MHz。

如果出于某种原因需要AIX,那么Power的重要性就不言而喻了。Power4和Power5都是高速、但复杂的采用乱序技术的RISC处理器,它结合了四路超标量执行机制和非常高的系统带宽。不过,Power6却回到了有序技术时代。原因何在?

一个答案就是,如果Power6的同步多线程效果好,那么对单一线程浪费执行资源就不用太担心:在这种情况下,只要同步运行两个线程就行。另外,为了进一步大幅提升性能,频率提高一倍、二级高速缓存增加一倍、缩短算术逻辑单元(ALU)的延迟等方面恐怕更关键。即使那样,浮点处理部件还会保留有一定的乱序执行功能——这是在通用处理器的浮点运算部分首次引入十进制浮点处理单元(FPU)。“同步双线程执行、负荷预测机制以及增强的数据和指令预取功能,提升了有序执行超标量核心的性能。”IBM是这么评价其新芯片的。

Power5+的五路无序执行被Power6的七路有序执行所取代,但即使如此,也有几个地方需要注意:Power5+一个线程每个周期最多只有五条指令,而Power6一个线程增加了二条指令,这对计算型线程和内存搜寻型线程组合来说更有优势。Power5+更关注内部资源,而Power6在大部分时候等待内存,所以每个周期两次操作完全够了。那么性能方面有什么提升呢?看一下基准测试specfp2006,频率为2.2GHz的Power5+在这方面能达到14.9,当然是在经过改动的Power5机器上实现的;而频率为4.7GHz的Power6能达到22.3,时钟频率提高了一倍多,性能提升却不到一半。

所以,Power6的7.9亿个晶体管分布在尺寸比较大的341平方毫米上,超过了Barcelona/Agena的283平方毫米,仅比尺寸庞大的安腾小了一点,它确实大幅提升了性能,尽管没有了乱序技术。虽然高速缓存和内存带宽随着时钟频率的提高都水涨船高,但是仍然可以说,在时钟频率相同情况下,重新使用有序技术会在处理单线程任务时导致性能下降30%左右。

为此,不得不等待更新的Power6系统以及下一版本AIX在编译器方面的进展,以减少这种性能损耗。不过对Power6来说,采用有序技术确实明显提升了处理器的性能。安腾同样采用了有序技术,但是至少到现在还没有看到明显的成效。x86恐怕再也不会出现有序技术。

不过,处理器技术的发展一日千里,Power6设计者不会坐井观天。英特尔公司的3.6GHz的Harpertown”Penryn“和AMD公司3GHz Barcelona处理器就会陆续面世,都会对IBM Power6构成重大挑战。IBM必须牢记: 对采用有序技术的这类处理器而言,随着每一代后续CPU的问世,在编译器方面需要做的工作更多。同时,并不是每个人都会有时间重新编译自己的应用程序等。

1、本站所有文本、信息、视频文件等,仅代表本站观点或作者本人观点,请网友谨慎参考使用。

2、本站信息均为作者提供和网友推荐收集整理而来,仅供学习和研究使用。

3、对任何由于使用本站内容而引起的诉讼、纠纷,本站不承担任何责任。

4、如有侵犯你版权的,请来信(邮箱:baike52199@gmail.com)指出,核实后,本站将立即删除。